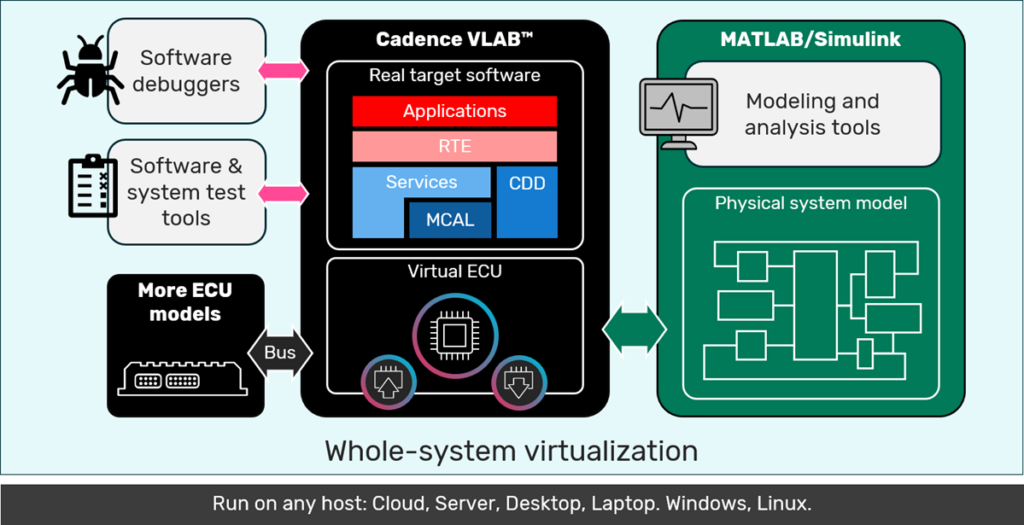

The Cadence VLAB team will be part of the Cadence team present at the MATLAB Expo Japan on May 26 in Tokyo. We will be demonstrating how MATLAB and Simulink models can be used to co-simulate with VLAB virtual development machines (VDMs), allowing software to be tested in a virtual hardware-in-the-loop environment.

Virtualized hardware-in-the-loop (HIL), processor-in-the-loop (PIL), and software-in-the-loop (SIL) techniques provide the ease of testing and development agility needed to realize software-defined vehicles (SDV). Virtualization provides developers and automated continuous integration and deployment (CI/CD) systems with instant access to any amount of hardware, avoiding the need to queue up tests for execution on limited physical test rigs.

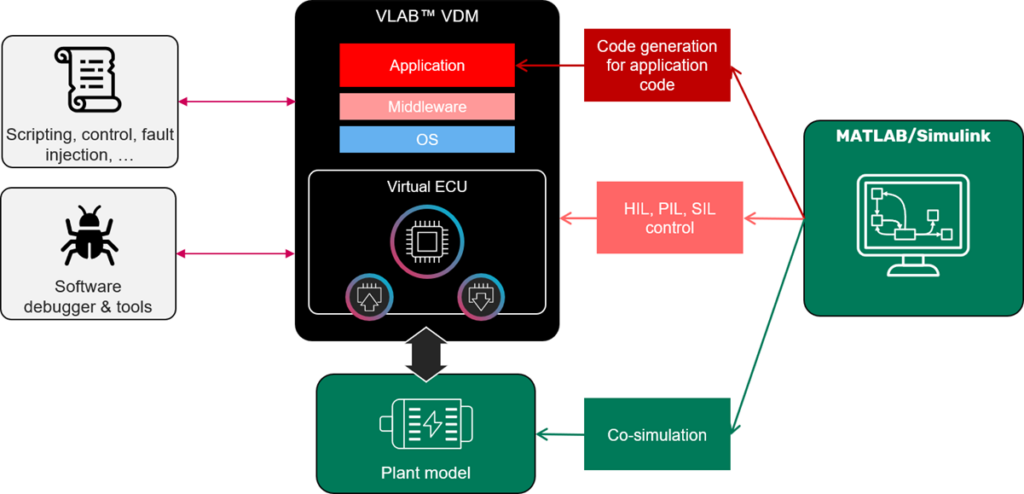

A VLAB VDM typically runs the complete software stack from the target system—applications, operating system, and drivers. The software is compiled for the target system, with no need for a special simulation variant. The VDM contains models of various input and output devices, both digital and analog. Sometimes it is as simple as a GPIO pin being driven in pulse-width modulated (PWM) mode. But it can also be analog signals or high-current drivers on a separate board, whatever is in the hardware.

From a VLAB perspective, it does not matter if the software being tested is written manually or generated from MATLAB/Simulink models. The software running on the VDM can be debugged and tested using standard software tools. It can be subjected to faults injected by VLAB scripts. This makes it possible to test the system under conditions like faulty sensors and actuators, exploring system stability and error handling. And, of course, challenging physical conditions can be simulated by the MATLAB/Simulink side.

Learn more about Cadence’s VLAB and automotive solutions.